1.算法描述

与很多的通信技术类似,扩频技术最初也应用于保密通信和制导系统等军事技术。除了在军事通信中的应用,扩频技术在无线通信领域也有发展。目前扩频通信技术已经在测距、卫星通信、GPS导航定位、移动通信、电子对抗、跟踪、遥控和蓝牙技术等方面广泛应用。扩频通信技术具有很多独特的优点:具有抗干扰能力强和截获率低等独特优点,而且具备码分多址(CDMA,Code Divided Multiple Access)或称为扩频多址(SSMA,SpreadSpectrumMultiple Access)的能力,因此广泛应用于商业、银行、宾馆、能源和交通业等行业。因为应用广泛受到世界各国的特别关注,尤其是在近年来随着超大规模的集成电路和微处理技术快速发展,使得扩频技术在各个行业得到更多的发展。随着数字技术的飞速发展,数字扩频技术不仅完成模拟扩频的所有功能,而且在性能和精度方面都有很大的优势,所以数字扩频技术将在未来被更广泛的应用。

在扩频通信技术中,发送端将原始信号的频带进行扩展,得到扩频信号,然后在接收端通过对信号进行解扩处理,恢复原始信号。根据通信系统产生的扩频方式,可以将扩频通信分为5类:直接序列扩展频谱(Direct Sequence Spread Spectrum Communication Systems)、频率跳变扩频通信系统(Frequecy Hopping Spread Spectrum Communication Systems,FH-SS)、跳时扩频通信系统(Time Hopping Spectrum Communication Systems,TH-SS)、线性脉冲调频系统(chirp)和混合扩频通信系统,扩频技术在未来无线通信技术中,仍是重要部分,很多方面需要继续去探索,因此扩频技术的研究不能停滞不前。

利用本原多项式产生伪随机序列用作扩频,通过同步模块对扩频后的信号进行捕获,通过直接序列解扩模块进行解扩。本文给出了编解码、扩频解扩、同步的整体方案,使用Quartus实现功能,并结合Matlab和ModelSim对模块进行调试和测试,实现扩频通信模块的搭建仿真,验证其设计的正确性。模块有:汉明编码模块、直接序列扩频模块、量化器模块、同步模块、直接序列解扩模块和汉明译码模块。

1.汉明编码模块

编码模块采用汉明码编码方式。汉明码是一种线性分组码。汉明码是指将数据信息码分成为长度为m的数据段,在每一段数据后面添加n位的校验码,这样编码方式为汉明码.

2. 扩频模块

扩频模块若采用直接序列扩频。直接序列扩频,简称直扩扩频(DSSS)。在发送端传送的数据信息需要经过信道编码后,与本原多项式产生的伪噪声序列进行模2加(异或)完成扩频,在接收端用相同的扩伪随机序列对其解扩,解扩后的数据进行译码,达到恢复原始数据信息的目的.

3.同步模块

同步模块若采用最小二乘法。最小二乘法是一种数学优化技术。它通过最小化误差的平方来和数据进行匹配。它可以简便地求得接收信号,并使得这些接收信号与伪随机序列之间误差的平方和为最小。

2.仿真效果预览

Quartus II 12.1 (64-Bit),

ModelSim-Altera 6.6d Starter Edition

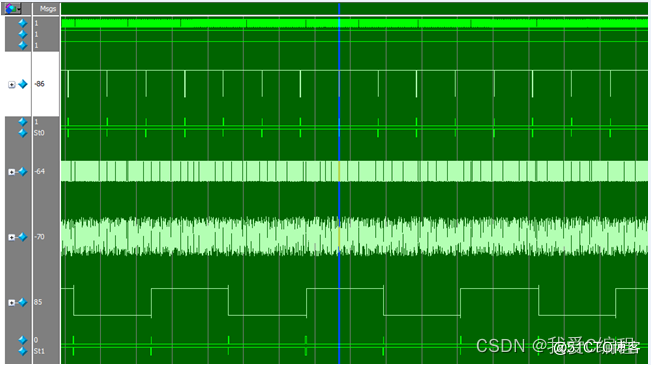

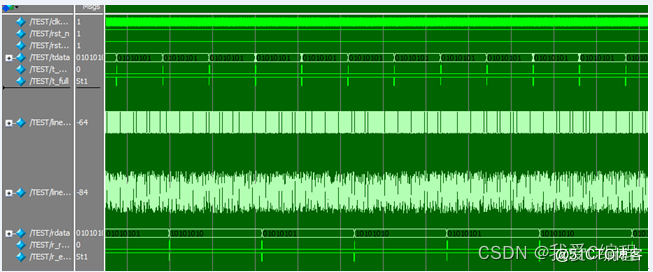

仿真结果如下:

3.Verilog核心程序

module tops(clk_10, rst_n, rst_n2,tdata, t_wrreq, t_full, rdata, r_rdreq,line_out, line_in, ............................................... ham_encoder ham_encoder_u1(//汉明编码 .clk_10(clk_10), .rst_n(rst_n), .hdata(hdata), .h_empty(h_empty), .h_rdreq(h_rdreq), .mdata(mdata), .m_empty(m_empty), .m_rdreq(m_rdreq) ); m_encoder m_encoder_u2(//m序列扩频 .clk_10(clk_10), .rst_n(rst_n), .mdata(mdata), .m_empty(m_empty), .m_rdreq(m_rdreq), .q_data(q_data) ); quantizer quantizer_u3(//量化 .clk_10(clk_10), .rst_n(rst_n), .qdata(q_data), .line_out(line_out) ); DSSSreceiver DSSSreceiver_u4(//接收器 .clk_10(clk_10), .rst_n(rst_n2), .line_in(line_in), .rdata(rdata), .r_rdreq(r_rdreq), .r_empty(r_empty) ); endmodule