1. 线负载模型

- 根据模型中提供的扇出-线网长度对应表,可以根据线网扇出负载估计线网长度。

- 根据线网长度和阻抗、容抗、面积对应表格计算线上参数和延时信息。

- 根据延时计算方式,主要有三种模型:

- worst_case_tree

- best_case_tree

- balanced_tree

set_wire_load_model

2. 时钟属性

- 时钟不确定性(uncertainty)包括skew和jitter。

2.1 时钟偏移(skew)

- 由于线网等延时,导致时钟信号到达寄存器口存在相位差。

- 其与时钟频率没有直接关系,与时钟线的长度及时钟线驱动的时序单元负载电容、个数有关。

2.2 时钟抖动(jitter)

- 不随时间积累,时而超前、时而滞后的偏移。与时钟频率也无直接关系。

- 包括随机抖动和固定抖动

- 随机抖动来源于:热噪声、Flicker Noise等,与电子器件和半导体器件的电子和空穴特性有关。选择合适的工艺可以得到更小的随机抖动。

- 固定抖动来源于:开关电源噪声、串扰、电磁干扰等。可以通过优化设计改善固定抖动;如选择合适的电源滤波方案、合理的PCB布局布线。

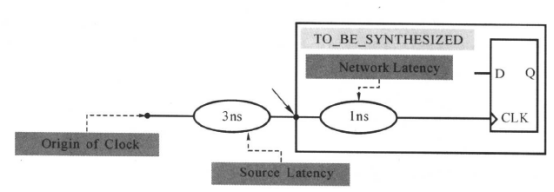

2.3 时钟延迟(latency)

- 时钟信号从时钟源(例如:晶振)触发到达触发器时钟端口的延时,为时钟延迟。

- 主要包括时钟源延迟(source latency)和 时钟网络延迟(network latency)。

- 主要包括时钟源延迟(source latency)和 时钟网络延迟(network latency)。

3. 时序约束实例

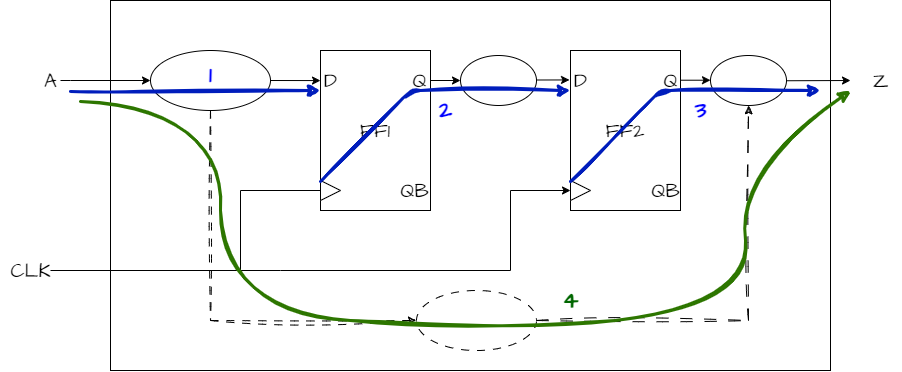

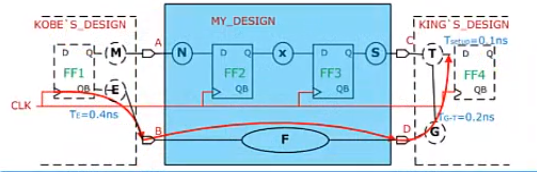

3.1 路径2的约束

- 为了满足FF2的建立时间要求,触发器翻转时间Tclk2q+寄存器和寄存器之前的组合逻辑延时Tlogic+FF2的建立时间 < 时钟周期。

- 保持时间一般是满足的,因为传输的延时(Tclk2q+Tlogic)一般都会大于触发器的保持时间。

3.2 路径1的约束

- 首先需要告诉DC被综合模块外的延时为Tclk_q+TM,留下的时间为Tclk-Tclk_q+TM,将其与Tn+Tsetup时间相比较,如果Tn太大,那么DC会对其进行优化,如果最优解也大于留下的时间,那么就会报错。

- 假设我们已知输入端口外部电路的延迟为4ns,那么可以使用DC的约束指令

set_input_delay -max 4 -clock CLK [get_ports A] set_input_delay 3.5 -max -clock clk1 [remove_from_collection [all_inputs][get_ports clk1]] # 命令表示从所有的输入端口中除掉时钟clk - 前面介绍的是不考虑不确定因素的情况,当考虑时钟不确定性,有以下分析

- 假设时钟不确定时间为U,假设触发器的建立时间为1ns,外部输入延时为D,那么内部N逻辑所允许的最大延迟S为:

- S = Tclk-D-U-1

- 假设时钟不确定时间为U,假设触发器的建立时间为1ns,外部输入延时为D,那么内部N逻辑所允许的最大延迟S为:

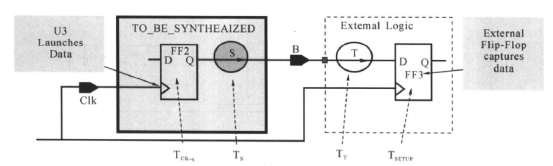

3.3 路径3的约束

- 告诉DC要综合的模块外部电路延时为TT+TFF3,setup,留下的时间为Tclk-TT-TFF3,setup时间,将这个值与Tclk_q+Ts相比较,如果Ts太大,那么DC会对其进行优化,如果最优解也大于留下的时间,那么就会报错。

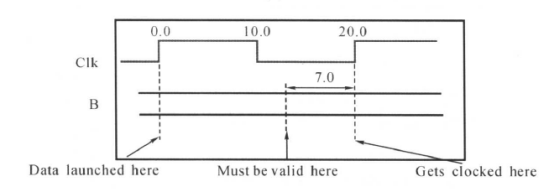

- 假设DC约束指令如下

create_clock -period 20 [get_ports Clk] set_output_delay -max 7.0 -clock Clk [get_ports B]

- 上面是没有考虑时钟不确定的,假设综合模块内部延时为S(包含T_clk2q和组合逻辑延时),外部输出延时为X(包括外部组合逻辑和后级寄存器的建立时间),时间不确定度为Y,时钟周期为T。

- 满足T-S-Y=X。

3.4 路径4的约束

- 分为两种情况

- 模块内部除了从输入到输出的组合逻辑外还有时序逻辑。

set_input_delay 0.4 -clock CLK -add_delay [get_ports B] set_output_delay 0.2 -clock CLK -add_delay [get_ports D] set_max_delay $CLK_PERIOD -from [get_ports B] -to [get_ports D]- DC计算T>E+F+U+G(其中U为不确定时间)。

- 模块内部都是组合逻辑,没有时序逻辑,这种需要使用虚拟时钟的概念。

- 模块内部除了从输入到输出的组合逻辑外还有时序逻辑。