芯片制造与测试技术杂谈

FinFET与芯片制程

芯片制造商已经在基于 10nm 和/或 7nm finFET 准备他们的下一代技术了,但我们仍然还不清楚 finFET 还能坚持多长时间、用于高端设备的 10nm 和 7nm 节点还能延展多久以及接下来会如何。

在 5nm、3nm 以及更小节点,半导体行业还面临着巨大的不确定性和许多难题。即使在今天,随着每个节点的工艺复杂度和成本的上升,传统的芯片尺寸缩减也在放缓。因此,能够负担先进节点芯片设计的客户越来越少。

理论上,正如

英特尔所定义的那样,finFET 有望延展到 5nm 节点。(一个完整延展的 5nm 工艺大致相当于代工厂的 3nm)。不管这些让人困惑的节点名称是啥,finFET 很可能将在 fin 宽度达到 5nm 时寿终正寝。所以在 5nm 或更先进的节点,芯片制造商将需要一种新的解决方案。否则传统的芯片缩放将会放缓或完全停滞。

一段时间以来,芯片制造商已经为 5nm 及以后节点探索了各种各样的

晶体管。到目前为止,仅有

三星提供过细节。在 5 月份,该公司推出了自己的技术路线图,其中包括在 2020 年之前实现一种 nanosheet FET。

其它芯片制造商也倾向于同一时间框架内的相似结构,即使它们还没有公开宣布它们的意图计划。 nanosheet FET 和其它变体、nanowire FET 都是属于环绕栅极(gate-all-around)类别。其它变体还包括hexagonal FET、nano-ring FET 和 nanoslab FET。

什么是FinFET?

FinFET称为鳍式场效应晶体管(Fin Field-Effect Transistor)是一种新的互补式金氧半导体(CMOS)晶体管。FET 的全名是“场效电晶体”,先从大家较耳熟能详的“MOS”来说明。MOS 的全名是“金属-氧化物-半导体场效电晶体(Metal Oxide Semiconductor Field Effect Transistor,MOSFET)”,构造如图一所示,左边灰色的区域(矽)叫做“源极(Source)”,右边灰色的区域(矽)叫做“汲极(Drain)”,中间有块金属(绿色)突出来叫做“闸极(Gate)”,闸极下方有一层厚度很薄的氧化物(黄色),因为中间由上而下依序为金属(Metal)、氧化物(Oxide)、半导体(Semiconductor),因此称为“MOS”。

图1

沟槽宽度的减小,可以带来如下的优点:

(1)沟槽宽度对应着D到S极的距离,沟槽宽度减小,载流子流动跨越沟道的导通时间减小,这样允许工作的开关频率就可以提高;

(2)沟槽宽度小,沟道完全开通所加的G极电压可以降低,导通更容易,开关损耗降低;

(3)沟槽宽度减小,沟道导通电阻降低,也更一进降低导通损耗。

正因为这些优点,也驱使半导体制造公司不断的采取新的工艺,追求更低的工艺尺寸,来提升半导体器件的性能、降低功耗。

图2:变形的平面横向导电MOSFET结构

图2右上角为平面MOSFET的结构,实际的结构稍微变形,如图2下方的所示,G极同样也是跨在D和S之间,G极下面为绝缘的氧化层。

从模拟或IP设计人员的角度来看,上述设计方法(鳍片由晶圆代工厂实施)并非首选模型。这些设计人员希望能获得更大的自由度,以减少渗漏、匹配驱动能力、提高频率响应以及推动电气和几何限制,而这些都是固定鳍片无法做到的。根据其性质,这种设计是定制的,而无法控制鳍片数量或大小对于其中很多设计人员来说是非常别扭。

图3

对于从28nm或以上工艺跳到FinFET工艺的定制、模拟或IP设计人员来说,这种设计是革命性的,但不一定是字面上的“全新改良”。虽然有工具创新来缓和这种过渡,进行这种设计的方法与其习惯的设计手法相比可能更显严格。采用传统MOSFET工艺,这些设计人员设计定制化的晶体管包括定制其尺寸和方向。对于FinFET,设计人员将通过更少的变量来达成所需的电气响应。可以通过FinFET 工艺来完成先进的模拟设计,但需要对设计方法进行重大改变,且可能需要更多的实验。

2、传统平面结构的限制

近些年来,半导体工艺不断的向着微型化发展,基于传统平面MOSFET结构的晶胞单元不断的缩小,漏、源的间距也不断的减小,G极下面的接触面积越来越小,G极的控制力就不断的减弱,带来的问题就是不加栅极电压时漏源极的漏电流增加,导致器件的性能恶化,同时增加了静态的功耗。

增加G极面积的方法,就必须采用新的结构,如三维结构。三维的G极结构有二种类型:一是双栅极结构,二是Fin型结构,也就是非常有名的鳍型结构,如下图所示。

(a):双栅极结构

G极不加电压 单G极加电压 双G极加电压

(b):导通沟道

图4:双栅极结构及导通沟道

双栅极结构形成二个沟道,减小沟道的导通电阻,增强了通流的能力和G极对沟道的控制能力。

图5:Fin鳍型结构

FinFET结构看起来像鱼鳍,所以也被称为鳍型结构,其最大的优点是Gate三面环绕D、S两极之间的沟道(通道),实际的沟道宽度急剧地变宽,沟道的导通电阻急剧地降低,流过电流的能力大大增强;同时也极大地减少了漏电流的产生,这样就可以和以前一样继续进一步减小Gate宽度。

参考链接:

https://www.sohu.com/a/108777952_467791

一颗芯片的前世今生:流片制造

一、绪论

今天讲讲芯片的流片制造那些事儿。这个流程的输入是设计的版图文件,输出是做好的芯片晶圆。

这是芯片的第四个流程。这块儿,国65nm这个量级的做的还可以,14nm应该SMIC也凑活,先进制程7乃至5nm的商业化基本是空白。属于真正被大洋彼岸卡脖子的部分。这篇文章科普一下整个制造流程。技术部分应该比较少,所以讲点儿故事。管中窥豹,故事不妨从台积电展开。

三、芯片的制造流程

那么台积电到底怎么用沙子把版图造成芯片的?这个流程的图是从intel 《From Sand to Silicon》这篇文章里贴的。

step1,挖沙子,然后做成硅锭

其中,硅要足够的纯,要9个9,99.9999999%纯度。为什么要用SI做芯片?也简单,硅是半导体,能做开关,世界上沙子也多,还容易提纯,与是就决定是它了。

step2, 硅锭切成硅片

将硅锭切成1mm左右一片片的wafer(晶圆)。晶圆尺寸有大有小,比如8inch, 12inch的晶圆,光刻的时候直接刻整个圆,然后切下来好多小芯片。

硅片切好以后,需要在上面氧化一层二氧化硅,用来做栅极。来看看下面的剖面图,红色的就是二氧化硅。

step3, 光刻

这个步骤首先在硅片上抹上一层光刻胶,一般来讲光一照,光刻胶就溶解(正胶)。然后用做好的掩模mask来照射wafer。

看上面这个剖面图,黄色的就是加入的光刻胶。黑色是根据版图制作出来的模板。然后用UV光去照,把光刻胶镂空。

step4, 刻蚀与粒子注入

这个步骤,用药水把oxide刻蚀了,然后把光刻胶洗掉,最后注入离子。

看剖面图。f就是刻好的oxide. 然后在洞里注入离子,形成源极和漏极。至此晶体管就造好了。

此处要插播一个小知识。平时说的工艺制程,比如28nm, 14nm指的是晶体管栅极宽度,也就是导电沟道的长度,不是指的线宽,最小线宽一般比制程要粗了现在。在图上标注了65nm指的是什么。

在GDS版图上是这个距离,下面画了个非门的版图。

step5 金属线制作

这个步骤主要是上硅片上连上金属线。这个过程依旧看下面的剖面图比较清楚。

看b图,首先在上面电镀一层金属,c图用光刻胶和掩膜版再刻蚀一遍得到d图,然后一层一层刻蚀叠加起来就行,层与层之间只有固定的通孔via用于连接。

step6 硅片测试与切片

接下来代工厂还要做几个事儿。

第一件事儿是先检查一下晶圆和芯片是不是好的。主要包含了两个测试。

WAT (Wafer Acceptance Test), 这个主要是测试一下晶圆的电学特性是不是正常的。WAT测试电路代工厂在流片的时候就直接加入到晶圆里了,主要包括了各种晶体管参数,比如阈值电压,漏电流,电阻,电容是不是正常的。WAT的测试向量是代工厂自己搞的。

CP(Chip Probing)测试。WAT测试没问题以后,接下来进行CP测试,先用探针看看芯片是不是好的,有问题的芯片直接扔掉,免得浪费封装成本。一般会用到前面讲的DFT三把斧,sacn chain, JTAG, BIST。CP测试向量由设计商提供。如果CP不合格,直接标记出来,扔掉。

CP测试完了以后,就把芯片按照划片槽切成一个个小的芯片,装盒。寄出来了。

四、总结

对芯片在代工厂的流程做了大概的讲解。实际上芯片的制作的工艺流程要复杂非常多,比如现在制程越来越小,光刻的时候量子隧穿效应非常严重,做出来模板肯定不是想想的镂空的窗花,这里只是讲了最重要最基础的步骤。这篇文章的输入是设计的GDS, 输出是一个个芯片裸片。这些裸片没办法直接接到PCB上的,需要经过后续的封装和测试,才算是真正的芯片。

来源:https://zhuanlan.zhihu.com/p/523181440

参考文献链接

https://mp.weixin.qq.com/s/y4-_c-vANkw9vCKz0gVctQ

关于“流片”

流片是什么?

流片(tape-out)是指通过一系列工艺步骤在流水线上制造芯片,是集成电路设计的最后环节,也就是送交制造。

流片即为"试生产",是把电路设计变成ASIC芯片的过程。即Fabless厂商设计完电路后,在所有检查和验证都正确无误的情况下,将最后的GDSII文件交由Foundrv厂先生产一部分样品芯片(通常为数十片或上百片不等),以检验每一个工艺步骤是否可行,以及电路是否具备所需的性能和功能。

tape是"磁带"的意思。早期进行芯片设计,都是以磁带来存储芯片设计数据的,因此称为tape-out。虽然目前多以电子文档提交数据,但这一称呼沿用至今。

tape-out是一个统称。细分来看,还有base tape-out、metal tape-out 和all-layer tape-out之分。

芯片制造包括多个工艺步骤,在制造时需要分层进行。其中,在FEOL工序生产的为baselayer(一般为晶体管等半导体器件),在BEOL工序生产的为metal layer (一般为金属布线层等)。

首次流片时,需要依次对所有的层进行生产加工。样片经测试后,如果发现需要进行很小的设计升级,或修正设计中的小错误,ECO阶段也许只需修改布线层就能实现,此时的tape-out被称为metal tape-out。但如果芯片必须进行重新设计、重新综合、布局布线,那芯片的所有层基本都会发生变化。base tape-out或all-layer tape-out意味着更长的周期和更高昂的成本。

流片成功or失败?

流片的目的是发现芯片在实际应用时存在的问题并进行解决。并非所有的流片都会成功。

如果样片测试成功,或通过小的修改即符合预期,就可以大规模地制造芯片,投入量产。反之,如果测试失败,可不是简单回头修改修改软件,等待再次流片这么简单。流片的成本是十分高昂的,如果连续两次以上流片失败,公司很可能会考虑取消该芯片的制造计划。因为继续下去投入的人力、物力和资金过多,即使最后流片成功也挽回不了损失。因此在流片之前,对设计的正确性进行充分的验证是非常必要的。

随着芯片密度的提高和设计复杂性的增加,对“流片"一次性成功的需求越来越迫切。一旦流片失败,轻则资金打水漂,重则公司直接倒闭。何降低流片?

为了减轻流片费用,MPW应运而生。

多项目晶圆(Multi Project Wafer, 简称MPW)就是将多个使用相同工艺的集成电路设计放在同一晶圆上流片,制造完成后,每个设计可以得到数十枚芯片样品,这一数量对于原型设计阶段的实验、测试已足够。

对于MPW流片,所有MPW项目参与者按照芯片面积分摊所产生的费用,仅为full mask流片费用的5%~10%,极大地降低了产品开发风险。MPW为小批量生产提供了有效的途径。

参考文献链接

如何降低流片成本?

芯片行业对于流片(Tape-out)都不陌生。

所谓流片,就是像流水线一样通过一系列工艺步骤制造芯片,简单来说就是芯片公司讲设计好的方案,交给晶圆制造厂,先生产少量样品,检测一下设计的芯片能不能用,根据测试结果决定是否要优化或大规模生产。所以为了测试集成电路设计是否成功,必须进行流片,这也是芯片设计企业一般都在前期需要投入很大成本的重要原因。

一颗芯片从设计到量产,流片是非常关键的环节。当芯片完全设计出来以后需要按照图纸在晶圆上进行蚀刻,采用什么样的制程工艺,多大尺寸的晶圆,芯片的复杂程度都会影响这颗芯片的流片成功率和成本,而且许多芯片都不是一次就能流片成功的,往往需要进行多次流片才能获得较为理想的效果。

但流片是一件非常烧钱的事,有芯片大厂算过一笔账,14nm工艺芯片,流片一次需要300万美元左右,7nm工艺芯片,流片一次需要3,000万美元,5nm工艺芯片,流片一次更是达到4,725万美元。可见,流片对于芯片设计企业来说是一笔巨大花费,尤其是对于行业中小企业来讲,实际流片的价格比大厂又高很多,让本不富裕的“生活”更是雪上加霜。

流片为什么这么贵?

那芯片流片的价格为什么这么贵?

这就要提到芯片的制造原理了。芯片制造要在很小的芯片里放上亿个晶体管,制造工艺已经到了纳米级,只能用光刻来完成。光刻就是用光刻出想要的图形,光刻需要用到掩膜版(又称光罩,Mask),掩膜版就是把设计好的电路图雕刻在上面,让光通过后,在晶圆上刻出图形。

流片贵,一方面是因为刚开始有许多工艺需要验证,从一个电路图到一块芯片,检验每一个工艺步骤是否可行,检验电路是否具备所要的性能和功能。芯片流片过程至少持续三个月(包括原料准备、光刻、掺杂、电镀、封装测试),一般要经过1,000多道工艺,生产周期较长,因此也是芯片制造中最重要最耗钱的环节。

如果流片成功,就可以据此大规模地制造芯片;反之,就需要找出其中的原因,并进行相应的优化设计。

其中,芯片流片贵,主要贵在掩膜版和晶圆,这两项价格不菲且都是消耗品,其中掩膜版最贵,一套中端工艺制程的掩膜版价格大约在50万美元左右,而一片晶圆的价额也在数千美元。

掩膜贵还是晶圆贵?

掩膜版是微电子制造过程中的图形转移工具或母版,其功能类似于传统照相机的“底片”,根据客户所需要的图形,通过光刻制版工艺,将微米级和纳米级的精细图案刻制于掩膜版基板上,是承载图形设计和工艺技术等内容的载体。

这种从掩膜版的图形转换到晶圆上的过程,有点类似印钞机的工作流程。把光刻机想象成印钞机,晶圆相当于印钞纸,掩膜就是印版,把钞票母版的图形印到纸张上的过程,就像光刻机把掩膜版上的芯片图形印到晶圆上一样。

掩膜版的价格主要取决于芯片所选用的“工艺节点”,工艺节点越高、流片价格就越贵。这是因为越先进的工艺节点,所需要使用的掩膜版层数就越多。据了解,在14nm工艺制程上,大约需要60张掩膜版,7nm可能需要80张甚至上百张掩膜版。

掩膜版层数多了,不仅仅是因为掩膜板的价格贵,还因为每多出一层 “掩膜板”,就要多进行一次“光刻”,就要再多涂抹一次 “光刻胶”,就要再多一次 “曝光”,然后再来一次 “显影” ...,整个流程下来耗费的成本就大大增加了。

据IBS数据显示,在16/14nm制程中,所用掩膜成本在500万美元左右,到7nm制程时,掩膜成本迅速升至1500万美元。

掩膜版的总体费用,包括石英,光刻胶等原材料的成本,Mask Writer和Inspection等机台的使用成本,另外还有掩膜版相关数据的生成,包括OPC、MDP等软件授权、服务器使用和人工开发成本等等。对于一款芯片,动辄几十层的掩膜版,需要如此多的步骤,设备、软件、人员缺一不可,费用自然昂贵。

据业内人士透露,某晶圆代工厂(Foundry) 40nm流片的光罩成本大约60-90万美元;进入量产之后,每片晶圆可能3000-4000美元左右,所以,当前期生产5-25片进行产品验证用,Mask成本是主要的;如果量产很多,Mask的成本平摊到每片晶圆以后就很少了,那么则是晶圆主导成本。准确的说应该是平均到每一颗芯片上的费用便宜了,而不是总的流片费用便宜了。

如何降低流片成本?

上述种种因素影响下,芯片流片费用成为摆在设计企业面前的一个难题。那么,面对流片价格高的问题,有没有什么办法来降低成本?

MPW (Multi Project Wafer) 就是一种可以帮助设计企业降低成本的流片方式。MPW是指由多个项目共享某个晶圆,同一次制造流程可以承担多个IC设计的制造任务,将多个使用相同工艺的集成电路设计放在同一晶圆上流片,制造完成后,每个设计可以得到数十片芯片样品,这一数量对于原型设计阶段的实验、测试已经足够。

通俗来讲就是几家公司或机构一起购买一套掩膜版,然后生产出来的同一片晶圆上会同时存在有好几款芯片,待晶圆切割后,再把各自的芯片“领回家”。而该次制造费用就由所有参加MPW的项目按照芯片面积分摊,极大地降低了产品开发风险。

MPW有一定的流程,通常由晶圆代工厂或者第三方服务机构来进行组织,各种工艺在某一年之中的MPW时间点是预先设定好的,通常是越先进的工艺,安排的MPW频率越高。晶圆代工厂事先会将晶圆划好多个区域并报价,各家公司根据自己情况去预订一个或多个区域。

这对参与者来说,在设计和开发方面有一定的进度压力。但是相比之下,MPW带来的好处是显而易见的,采用多项目晶圆能够降低芯片的生产成本,为设计人员提供实践机会,并促进了芯片设计的成果转化,对IC设计人才的培训,中小设计公司的发展,以及新产品的开发研制都有相当大的促进作用。

对比来看,共享Mask的好处就是省钱,但是可能要等代工厂的时间节点,需要更多的时间。对于那些不差钱或赶时间的企业当然可以自己利用一套Mask(Full- Mask,全掩膜),制造流程中的全部掩膜都为自己的设计来服务,通常用于设计定型后的量产阶段。机器一响,黄金万两。

因此,提升一次流片的成功率,也是降低流片成本的重要因素。

实际上,对于大部分的中小企业来说,除了价格以外,在流片或量产环节还面临着包括产能、交期在内的诸多挑战:

1.对Foundry体系不了解,缺乏工艺选型的经验和Foundry打交道的经验;

2.主流Foundry准入门槛高,新兴玩家难以申请预期的工艺或支持,沟通成本高;

3.缺乏系统的供应链管理能力,尤其在量产产能爬坡阶段,对产能、交期、质量过于乐观;

4.产能紧缺情况下,缺乏备货机制,恐慌性下单或有了订单再下单导致产能跟不上市场需求。此外,交期的变化、产能的波动都会大大增加初创公司与晶圆代工厂的沟通成本,降低效率。

摩尔精英,为客户芯片流片保驾护航

对此,中小芯片设计企业可以寻求有资源、有经验的第三方流片服务平台进行合作,一同来解决遇到的供应链难题。

以摩尔精英流片服务,可以提供完整的工艺平台,对接数十家主流晶圆代工厂,提供MPW、Full-mask及量产在内的不同工艺节点的流片服务,能够显著降低客户的商务成本和沟通成本。

另一方面,凭借自建的专业流片FAE团队,不仅为合作晶圆代工厂提供长尾客户的高效支持管理,也帮助中小公司的产品快速得到支持,协助客户选择最优工艺,并保障客户的数据安全。

摩尔精英流片服务参考流程

在产能方面,利用摩尔精英的know-how协助中小客户去争取产能(包括大订单、订单量趋势、提前排队、及时跟踪产能动态等),帮助客户降低成本和缩短芯片研发周期。

摩尔精英自2018年升级业务模式,投资建设2万平自有封测产能,合肥快封工程中心、重庆快封工程中心、无锡SiP封测中心相继投入运营,服务能力,聚焦SiP封装、Flip-chip封装、快速工程封装,和基于自主ATE设备的量产测试服务。通过自有的封测一体交付能力,也为客户提供了从原型到量产的快速通道。

参考文献链接

龙芯2K2000集成两个基于自主龙架构的LA364处理器核,共享2MB二级缓存,典型工作频率1.5GHz,SPEC2006INT(base)单核定/浮点分值达到13.5/14.9分。

同时,龙芯2K2000还集成了龙芯自主研发的LG120 GPU图形核心,并进一步优化了图形算法和性能。

I/O接口非常丰富,支持64位DDR4-2400 ECC内存、PCIe 3.0、SATA 3.0、USB 3.0/2.0、HDMI/DVO显示接口、GNET/GMAC网络接口、音频接口、SDIO/eMMC等接口。

此外还集成了安全可信模块,Rapid IO、TSN、CAN等特色工业接口。

塑封版本采用FC-BGA883封装,长宽尺寸为27 x 27mm,同时支持高等级封装。

得益于片内丰富的低功耗控制方法,龙芯2K2000功耗的可伸缩性良好,初步测试结果显示在高性能模式下约为9W,平衡性能模式下约为4W,可满足多种应用场景的需求。

龙芯中科表示,将在龙芯2K2000设计平台的基础上,开发一系列针对不同细分领域的SoC芯片,更精准地服务客户需求。

随着龙芯2K2000的推出,龙芯自主指令系统LoongArch(简称龙架构)的产品,已经形成了工控型1C102、1C103,工控/通用型2K0500、2K1000LA、2K1500、2K2000,消费型3A5000,服务器型3C5000、3D5000等组成的完整系列,性能从高到低全覆盖。

说完硬的,再看看软的。

1月9日,第二届操作系统产业峰会上,中国工程院院士郑纬民在开篇致辞中强调:“自主创新是攀登世界科技高峰的必经之路,没有第二条路。操作系统作为关键核心技术起到战略性、支撑性、全局性的作用,必须以大气力加以突破。”

峰会上,麒麟软件操作系统上新,展示了最新的技术实力和研究成果。

1、银河麒麟高级服务器操作系统V10 SP3

一款支持行业专用的软件系统,尤其是针对企业级关键业务,为企业上云提供更高安全等级、更合规的产品和服务,标志着银河麒麟操作系统面向云化的全面突破。

内核由麒麟软件深度自研开发,针对指令级别进行创新优化,性能表现提升5%以上。

尤其针对企业关键业务场景进行性能调优,在数据库读写、响应时间、计算负载等能力上表现远超竞品。

在安全性能上,从硬件层到服务层打通,形成一体化的可信安全体系。

与其他配套扩展软件结合,可以共同服务传统业务应用、系统迁移、云计算、大数据、高可用、虚拟化、人工智能7大场景。

CPU处理器支持海光、兆芯、申威、飞腾、鲲鹏、龙芯等六大平台,也支持Intel、AMD。

2、银河麒麟嵌入式操作系统V10

一款面向物联网、工业互联网场景的安全实时嵌入式操作系统,具备信息安全、多域隔离、云边端协同、支持多样性算力等特点,可满足嵌入式场景对操作系统小型化、可靠性、安全性、实时性、互联性的需求。

具有多域隔离、内生安全、强实时性、AI智能化、工业稳定、泛在连接、按需定制、生态丰富八大产品特性,可广泛应用于多个行业场景。

例如公共交通行业地铁AFC、ETC收费,工业制造行业机器人控制及产品质检,金融科技行业智慧网点、智慧柜员机、展业平板等智能终端,能源电力行业DCS、DPU场景,汽车电子行业智能驾驶、车联网,数字通信行业智能网关,医疗卫生行业自助机具和医疗设备,智慧城市领域数字政府、智能园区等。

3、星光麒麟操作系统1.0

具备弹性扩展、内生安全、智能互联、统一框架”四大特性,攻克了一系列关键技术。

例如,全系统采用组件化设计,充分发挥了H5优势;

实现桌面端的软硬一体可信安全体系,完成可信启动支持;

智能互联支持智联相机、智联记事本两个多端协同应用,积累了支持分布式设备安全认证、互连互通和数据安全传输的SDK接口,并为AI交互体系构建SDK;

实现了安卓应用在H5桌面上的融合,完成了统一框架上的准备。

系统已全面适配、覆盖国产主流移动芯片,基于Linux+H5技术路线,同时融合了AOSP软件栈来支持安卓应用生态。

另外发布的还有银河麒麟系统升级管理平台,这是首款国产服务器操作系统集约化管理平台创新产品。

它拥有自动化漏洞发现与补丁安装、精细化系统配置管控两大核心功能,现已纳管超10000套银河麒麟服务器操作系统环境且稳定运行。

漏洞修复智能化一站式管理功能,可通过平台查看纳管主机漏洞情况数据仪表,直观展示纳管主机漏洞管理情况;

通过标准库和配置项两级控制进行配置管理,平台支持其他操作系统向麒麟服务器操作系统的迁移。

参考文献链接

从设计到流片丨IC设计全流程及要用到的EDA工具

IC前端设计(逻辑设计)和后端设计(物理设计)的区分:以设计是否与工艺有关来区分二者;从设计程度上来讲,前端设计的结果就是得到了芯片的门级网表电路。

设计中使用的EDA工具如下:

1、架构的设计与验证按照要求,对整体的设计划分模块。

架构模型的仿真可以使用Synopsys公司的CoCentric软件,它是基于System C的仿真工具。

2、HDL设计输入设计输入方法有:HDL语言(Verilog或VHDL)输入、电路图输入、状态转移图输入。使用的工具有:Active-HDL,而RTL分析检查工具有Synopsys的LEDA。

3、前仿真工具(功能仿真)初步验证设计是否满足规格要求。使用的工具有:Synopsys的VCS,Mentor的ModelSim,Cadence的Verilog-XL,Cadence的NC-Verilog。

4、逻辑综合将HDL语言转换成门级网表Netlist。综合需要设定约束条件,就是希望综合出来的电路在面积,时序等目标参数上达到的标准;逻辑综合需要指定基于的库,使用不同的综合库,在时序和面积上会有差异。逻辑综合之前的仿真为前仿真,之后的仿真为后仿真。使用的工具有:Synopsys的Design Compiler,Cadence的 PKS,Synplicity的Synplify等。

5、静态时序分析工具(STA)在时序上,检查电路的建立时间(Setuptime)和保持时间(Hold time)是否有违例(Violation)。使用的工具有:Synopsys的Prime Time。

6、形式验证工具在功能上,对综合后的网表进行验证。常用的就是等价性检查(Equivalence Check)方法,以功能验证后的HDL设计为参考,对比综合后的网表功能,他们是否在功能上存在等价性。这样做是为了保证在逻辑综合过程中没有改变原先HDL描述的电路功能。使用的工具有:Synopsys的Formality

后端相应的流程如下

1、数据准备

对于 CDN 的 Silicon Ensemble而言,后端设计所需的数据主要有是Foundry厂提供的标准单元、宏单元和I/O Pad的库文件,它包括物理库、时序库及网表库,分别以.lef、.tlf和.v的形式给出。前端的芯片设计经过综合后生成的门级网表,具有时序约束和时钟定义的脚本文件,由此产生的约束文件以及定义电源Pad的DEF(Design Exchange Format)文件。(对synopsys 的Astro 而言, 经过综合后生成的门级网表,时序约束文件 SDC 是一样的,Pad的定义文件–tdf , .tf 文件 --technology file,Foundry厂提供的标准单元、宏单元和I/O Pad的库文件 就与FRAM, CELL view, LM view形式给出(Milkway 参考库 and DB, LIB file)

2、布局规划

主要是标准单元、I/O Pad和宏单元的布局。I/OPad预先给出了位置,而宏单元则根据时序要求进行摆放,标准单元则是给出了一定的区域由工具自动摆放。布局规划后,芯片的大小,Core的面积,Row的形式、电源及地线的Ring和Strip都确定下来了。如果必要 在自动放置标准单元和宏单元之后, 可以先做一次PNA(power network analysis)–IR drop and EM 。

3、Placement -自动放置标准单元

布局规划后,宏单元、I/O Pad的位置和放置标准单元的区域都已确定,这些信息SE(Silicon Ensemble)会通过DEF文件传递给PC(Physical Compiler),PC根据由综合给出的.DB文件获得网表和时序约束信息进行自动放置标准单元,同时进行时序检查和单元放置优化。如果用的是PC +Astro,那可用write_milkway, read_milkway 传递数据。

4、时钟树生成(CTS Clock tree synthesis)

芯片中的时钟网络要驱动电路中所有的时序单元,所以时钟源端门单元带载很多,其负载延时很大并且不平衡,需要插入缓冲器减小负载和平衡延时。时钟网络及其上的缓冲器构成了时钟树。一般要反复几次才可以做出一个比较理想的时钟树—Clock skew.

5、STA 静态时序分析和后仿真 时钟树插入后,每个单元的位置都确定下来了,工具可以提出Global Route形式的连线寄生参数,此时对延时参数的提取就比较准确了。SE把.V和.SDF文件传递给PrimeTime做静态时序分析。确认没有时序违规后,将这来两个文件传递给前端人员做后仿真。对Astro 而言,在detail routing 之后,用starRC XT 参数提取,生成的SPEF文件传递给PrimeTime做静态时序分析,那将会更准确。

6、ECO(Engineering Change Order)

针对静态时序分析和后仿真中出现的问题,对电路和单元布局进行小范围的改动。

7、Filler的插入(padfliier, cell filler)

Filler指的是标准单元库和I/O Pad库中定义的与逻辑无关的填充物,用来填充标准单元和标准单元之间,I/O Pad和I/O Pad之间的间隙,它主要是把扩散层连接起来,满足DRC规则和设计需要。

8、布线(Routing)

布线是指在满足工艺规则和布线层数限制、线宽、线间距限制和各线网可靠绝缘的电性能约束的条件下,根据电路的连接关系将各单元和I/O Pad用互连线连接起来,这些是在时序驱动(Timing driven ) 的条件下进行的,保证关键时序路径上的连线长度能够最小。

9、Dummy Metal的增加 Foundry厂都有对金属密度的规定,使其金属密度不要低于一定的值,以防在芯片制造过程中的刻蚀阶段对连线的金属层过度刻蚀从而降低电路的性能。加入Dummy Metal是为了增加金属的密度。

10、DRC和LVS DRC是对芯片版图中的各层物理图形进行设计规则检查(spacing ,width),它也包括天线效应的检查,以确保芯片正常流片。LVS主要是将版图和电路网表进行比较,来保证流片出来的版图电路和实际需要的电路一致。DRC和LVS的检查–EDA工具Synopsy hercules/ mentor calibre/ CDN Dracula进行的。Astro also include LVS/DRC check commands。

11、Tape out

在所有检查和验证都正确无误的情况下把最后的版图GDSⅡ文件传递给Foundry厂进行掩膜制造,也就是送去流片了。

参考文献链接

芯片封测技术

长电科技是全球领先的集成电路制造和技术服务提供商,提供全方位的芯片成品制造一站式服务,包括集成电路的系统集成、设计仿真、技术开发、产品认证、晶圆中测、晶圆级中道封装测试、系统级封装测试、芯片成品测试并可向世界各地的半导体客户提供直运服务。

通过高集成度的晶圆级(WLP)、2.5D/3D、系统级(SiP)封装技术和高性能的倒装芯片和引线互联封装技术,长电科技的产品、服务和技术涵盖了主流集成电路系统应用,包括网络通讯、移动终端、高性能计算、车载电子、大数据存储、人工智能与物联网、工业智造等领域。长电科技在全球拥有23000多名员工,在中国、韩国和新加坡设有六大生产基地和两大研发中心,在逾22个国家和地区设有业务机构,可与全球客户进行紧密的技术合作并提供高效的产业链支持。

2.5/3D集成技术

随着市场对便携式移动数据访问设备的需求快速增长,市场对功能融合和封装复杂性的要求也在提升。同时对更高集成度,更好电气性能、更低时延,以及更短垂直互连的要求,正在迫使封装技术从 2D 封装向更先进的 2.5D 和 3D 封装设计转变。为了满足这些需求,各种类型的堆叠集成技术,用于将多个具有不同功能的芯片,集成到越来越小的尺寸中。

长电技术优势

长电科技积极推动传统封装技术的突破,率先在晶圆级封装、倒装芯片互连、硅通孔 (TSV) 等领域中,采用多种创新集成技术,以开发差异化的解决方案,帮助客户在其服务的市场中取得成功。

解决方案

应用市场

晶圆级封装技术

晶圆级封装(WLP)与扇出封装技术

当今的消费者正在寻找性能强大的多功能电子设备,这些设备不仅要提供前所未有的性能和速度,还要具有小巧的体积和低廉的成本。这给半导体制造商带来了复杂的技术和制造挑战,试图寻找新的方法,在小体积、低成本的器件中,提供更出色的性能和功能。

长电技术优势

长电科技在提供全方位的晶圆级技术解决方案平台方面,处于行业领先地位,提供的解决方案,包括扇入型晶圆级封装 (FIWLP)、扇出型晶圆级封装 (FOWLP)、集成无源器件 (IPD)、硅通孔 (TSV)、包封芯片封装 (ECP)、射频识别 (RFID)。

解决方案

应用市场

系统级封装技术

系统级封装(SiP)

半导体公司不断面临复杂的集成挑战,因为消费者希望电子产品体积更小、速度更快、性能更高,并将更多功能集成到单部设备中。半导体封装对于解决这些挑战具有重大影响。当前和未来对于提高系统性能、增加功能、降低功耗、缩小外形尺寸的要求,需要一种被称为系统集成的先进封装方法。

系统集成可将多个集成电路 (IC) 和元器件,组合到单个系统或模块化子系统中,以实现更高的性能、功能和处理速度,同时大幅降低电子器件内部的空间要求。

长电技术优势

长电科技在SiP封装的优势,体现在3种先进技术:双面塑形技术、EMI电磁屏蔽技术、激光辅助键合(LAB)技术。

l 双面成型有效地降低了封装的外形尺寸,缩短了多个裸芯片和无源器件的连接,降低了电阻,并改善了系统电气性能。

l 对于EMI屏蔽,JCET使用背面金属化技术,有效地提高热导率和EMI屏蔽。

l JCET使用激光辅助键合,克服传统的回流键合问题,例如 CTE不匹配,高翘曲,高热机械应力等导致可靠性问题。

解决方案

应用市场

倒装封装技术

技术

倒装封装技术

在倒装芯片封装中,硅芯片使用焊接凸块而非焊线直接固定在基材上,提供密集的互连,具有很高的电气性能和热性能。倒装芯片互连实现了终极的微型化,减少了封装寄生效应,并且实现了其他传统封装方法无法实现的芯片功率分配和地线分配新模式。

长电技术优势

长电科技提供丰富的倒装芯片产品组合,从搭载无源元器件的大型单芯片封装,到模块和复杂的先进 3D 封装,包含多种不同的低成本创新选项。

解决方案

应用市场

焊线封装技术

焊线形成芯片与基材、基材与基材、基材与封装之间的互连。焊线被普遍视为最经济高效和灵活的互连技术,目前用于组装绝大多数的半导体封装。

长电技术优势

长电科技可以使用金线、银线、铜线等多种金属进行焊线封装。作为金线的低成本替代品,铜线正在成为焊线封装中首选的互连材料。铜线具有与金线相近的电气特性和性能,而且电阻更低,在需要较低的焊线电阻,以提高器件性能的情况下,这将是一大优势。长电科技可以提供各类焊线封装类型,最大程度地节省物料成本,从而实现最具成本效益的铜焊线解决方案。

解决方案

应用市场

MEMS与传感器

随着消费者对能够实现传感、通信、控制应用的智能设备的需求日益增长,MEMS 和传感器因其更小的尺寸、更薄的外形和功能集成能力,正在成为一种非常关键的封装方式。MEMS 和传感器可广泛应用于通信、消费、医疗、工业和汽车市场的众多系统中。

长电技术优势

凭借技术组合和专业 MEMS 团队,长电科技能够提供全面的一站式解决方案,为量产提供支持,服务包括封装协同设计、模拟、物料清单 (BOM) 验证、组装、质量保证和内部测试解决方案。长电科技能够为客户的终端产品提供更小外形尺寸、更高性能、更低成本的解决方案。创新集成解决方案,能够帮助企业实现 MEMS 和传感器应用的尺寸、性能和成本要求。

解决方案

应用市场

参考链接:

揭秘芯片制造心脏EDA产业,国产路在何方?

EDA(电子设计自动化)是芯片之母,是芯片产业皇冠上的明珠:EDA软件工具涵盖了IC设计、布线、验证和仿真等所有方面。EDA是集成电路设计必需、也是最重要的软件工具,EDA产业是IC设计最上游、最高端的产业。

国内EDA产业发展从上世纪八十年代中后期开始,本土EDA企业有华大九天、芯禾科技、广立微电子、博达微科技、概伦电子、蓝海微科技、奥卡思微电等七家。这些企业虽然产品不够齐全、集成度不够高,但在点工具上取得了一定的成绩。其中,华大九天是全球唯一的能够提供全流程FPD设计解决方案的供应商,获得了大部分知名面板厂的市场份额。

EDA全景概述:IC设计全流程

何谓EDA?EDA是电子设计自动化(Electronic

Design Automation)的简称,是从计算机辅助设计(CAD)、计算机辅助制造(CAM)、计算机辅助测试(CAT)和计算机辅助工程(CAE)概念发展而来。

▲EDA历史沿革

IC产业链:芯片产业链包括设计、制造、封装、测试、销售,芯片核心实力重心在芯片设计,而芯片设计离不开芯片设计软件EDA,EDA可谓是芯片产业链“任督二脉”。

芯片设计流程:芯片设计可分为前端和后端,前端主要负责逻辑实现,后端跟工艺紧密结合。

▲芯片产业链各流程主要企业

参考链接:

FinFET与芯片制程

芯片制造商已经在基于 10nm 和/或 7nm finFET 准备他们的下一代技术了,但仍然还不清楚 finFET 还能坚持多长时间、用于高端设备的 10nm 和 7nm 节点还能延展多久以及接下来会如何。

在 5nm、3nm 以及更小节点,半导体行业还面临着巨大的不确定性和许多难题。即使在今天,随着每个节点的工艺复杂度和成本的上升,传统的芯片尺寸缩减也在放缓。因此,能够负担先进节点芯片设计的客户越来越少。

理论上,正如

英特尔所定义的那样,finFET 有望延展到 5nm 节点。(一个完整延展的 5nm 工艺大致相当于代工厂的 3nm)。不管这些让人困惑的节点名称是啥,finFET 很可能将在 fin 宽度达到 5nm 时寿终正寝。所以在 5nm 或更先进的节点,芯片制造商将需要一种新的解决方案。否则传统的芯片缩放将会放缓或完全停滞。

一段时间以来,芯片制造商已经为 5nm 及以后节点探索了各种各样的

晶体管。到目前为止,仅有

三星提供过细节。在 5 月份,该公司推出了自己的技术路线图,其中包括在 2020 年之前实现一种 nanosheet FET。

其它芯片制造商也倾向于同一时间框架内的相似结构,即使它们还没有公开宣布它们的意图计划。 nanosheet FET 和其它变体、nanowire FET 都是属于环绕栅极(gate-all-around)类别。其它变体还包括hexagonal FET、nano-ring FET 和 nanoslab FET。

什么是FinFET?

FinFET称为鳍式场效应晶体管(Fin Field-Effect Transistor)是一种新的互补式金氧半导体(CMOS)晶体管。FET 的全名是“场效电晶体”,先从大家较耳熟能详的“MOS”来说明。MOS 的全名是“金属-氧化物-半导体场效电晶体(Metal

Oxide Semiconductor Field Effect Transistor,MOSFET)”,构造如图一所示,左边灰色的区域(矽)叫做“源极(Source)”,右边灰色的区域(矽)叫做“汲极(Drain)”,中间有块金属(绿色)突出来叫做“闸极(Gate)”,闸极下方有一层厚度很薄的氧化物(黄色),因为中间由上而下依序为金属(Metal)、氧化物(Oxide)、半导体(Semiconductor),因此称为“MOS”。

图1

沟槽宽度的减小,可以带来如下的优点:

(1)沟槽宽度对应着D到S极的距离,沟槽宽度减小,载流子流动跨越沟道的导通时间减小,这样允许工作的开关频率就可以提高;

(2)沟槽宽度小,沟道完全开通所加的G极电压可以降低,导通更容易,开关损耗降低;

(3)沟槽宽度减小,沟道导通电阻降低,也更一进降低导通损耗。

正因为这些优点,也驱使半导体制造公司不断的采取新的工艺,追求更低的工艺尺寸,来提升半导体器件的性能、降低功耗。

图2:变形的平面横向导电MOSFET结构

图2右上角为平面MOSFET的结构,实际的结构稍微变形,如图2下方的所示,G极同样也是跨在D和S之间,G极下面为绝缘的氧化层。

从模拟或IP设计人员的角度来看,上述设计方法(鳍片由晶圆代工厂实施)并非首选模型。这些设计人员希望能获得更大的自由度,以减少渗漏、匹配驱动能力、提高频率响应以及推动电气和几何限制,而这些都是固定鳍片无法做到的。根据其性质,这种设计是定制的,而无法控制鳍片数量或大小对于其中很多设计人员来说是非常别扭。

图3

对于从28nm或以上工艺跳到FinFET工艺的定制、模拟或IP设计人员来说,这种设计是革命性的,但不一定是字面上的“全新改良”。虽然有工具创新来缓和这种过渡,进行这种设计的方法与其习惯的设计手法相比可能更显严格。采用传统MOSFET工艺,这些设计人员设计定制化的晶体管包括定制其尺寸和方向。对于FinFET,设计人员将通过更少的变量来达成所需的电气响应。可以通过FinFET 工艺来完成先进的模拟设计,但需要对设计方法进行重大改变,且可能需要更多的实验。

2、传统平面结构的限制

近些年来,半导体工艺不断的向着微型化发展,基于传统平面MOSFET结构的晶胞单元不断的缩小,漏、源的间距也不断的减小,G极下面的接触面积越来越小,G极的控制力就不断的减弱,带来的问题就是不加栅极电压时漏源极的漏电流增加,导致器件的性能恶化,同时增加了静态的功耗。

增加G极面积的方法,就必须采用新的结构,如三维结构。三维的G极结构有二种类型:一是双栅极结构,二是Fin型结构,也就是非常有名的鳍型结构,如下图所示。

(a):双栅极结构

G极不加电压 单G极加电压 双G极加电压

(b):导通沟道

图4:双栅极结构及导通沟道

双栅极结构形成二个沟道,减小沟道的导通电阻,增强了通流的能力和G极对沟道的控制能力。

图5:Fin鳍型结构

FinFET结构看起来像鱼鳍,所以也被称为鳍型结构,其最大的优点是Gate三面环绕D、S两极之间的沟道(通道),实际的沟道宽度急剧地变宽,沟道的导通电阻急剧地降低,流过电流的能力大大增强;同时也极大地减少了漏电流的产生,这样就可以和以前一样继续进一步减小Gate宽度。

参考链接:

https://www.sohu.com/a/108777952_467791

芯片量产服务

芯原的芯片量产服务范围包括根据客户需求,委外完成晶圆制造、封装、测试、产品认证和失效分析等服务,并提供以上过程中的生产管理服务。芯原的芯片量产服务以高质量和快速响应为客户产品的制造提供支持。

芯原根据每个客户的独特需求,识别和选择最合适的代工厂与工艺技术,以提供性能、成本和质量均衡的解决方案,从而交付给客户具竞争力的芯片产品。

了解更多

芯原的封装解决方案可实现实时芯片封装板设计微调和工艺问题快速处理。在设计、模拟和工程方面的专业知识可确保高效的封装开发和生产管理。

了解更多

芯原的测试开发服务缩小了设计和测试之间的差距,通过在项目设计阶段尽早参与测试,为客户提供快速的项目周转并确保测试质量。

了解更多

芯原凭借多年来与国内外领先工厂合作的经验,可协助客户建立全面、高效与可靠的芯片生产管理系统,从而提升客户产品的品质竞争力。

晶圆生产服务

芯原根据每个客户的独特需求,识别和选择最合适的代工厂与工艺技术,以提供性能、成本和质量均衡的解决方案,从而交付给客户最具竞争力的芯片产品。

芯原与战略代工合作伙伴密切合作,成功完成了数百个项目。 芯原提供广泛且灵活的生产支持,可帮助客户完成样片流片,以及小批量和大批量芯片生产。还支持设备调校和工艺优化,以提高产品性能和产量;提供产量监控和分析,以实现高效的产量提升,加快客户产品的上市周期。

测试服务

芯原的测试开发服务缩小了设计和测试之间的差距,通过在项目设计阶段尽早参与测试,为客户提供快速的项目周转并确保测试质量。芯原多年来在可测性设计、设计向量转换流程、在线调试以及对各种测试平台的支持方面累积了丰富的经验,可确保从设计到生产的顺利转换,并满足不同的成本要求。

- 定义测试计划,包括SCAN、MBIST、BSD和IP测试计划

- 测试硬件设计,包括探针卡、FT测试板

- 专业的设计向量转换工具

- 测试程序的开发调试与发布,以及量产优化

-

高速IP接口测试 - 生产回路

高速接口测试 - 锁相环IP性能测试 - 眼图,Jitter和DSSC - 扩频幅度

质量与可靠性

全面质量管理

芯原凭借多年来与国内外领先工厂合作的经验,可协助客户建立全面、高效与可靠的芯片生产管理系统,从而提升客户产品的品质竞争力。

芯原的生产服务内容涵盖晶圆制造、芯片封装、针测与成品测试、物流出货,以及贯穿整个设计开发和生产过程的质量管理系统、可靠性保证和供应链管理。

质量管理体系

芯原从2006年5月起在上海取得ISO9001认证,并于2010年11月开始实施台湾业务。此后,芯原持续每年接受第三方监督审核,以及每三年进行换证审核。公司于2017年11月取得ISO9001:2015版认证并维持至今。

信息安全管理系统

芯原已在公司内部建立了信息安全管理系统。从2008年1月起在上海取得ISO27001认证,此后,持续每年接受第三方监督审核,以及每三年进行换证审核。公司于2015年11月取得ISO27001:2013版认证并维持至今。

可靠性

全面的可靠性鉴定测试计划为芯原的可靠性保证提供支撑。芯原在严格执行相关计划的同时,还持续实施改进,以满足客户需求。

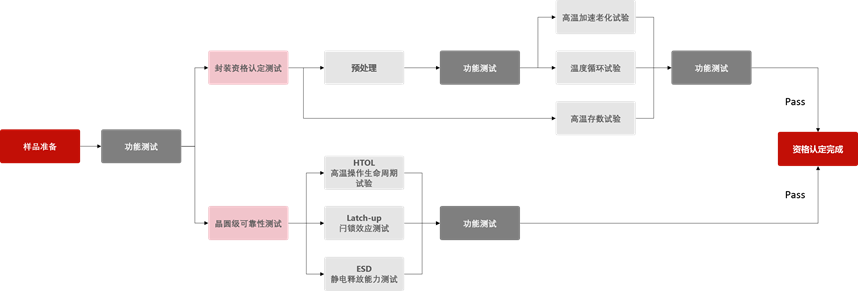

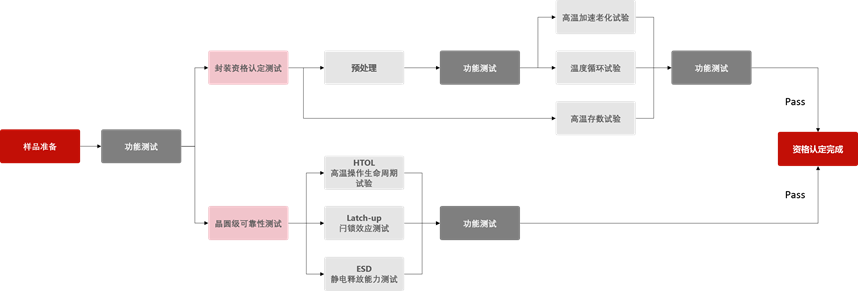

通用的可靠性鉴定测试流程和参考标准如下图所示。具体细节将由现场应用支持人员和客户共同按需制定。

先进封装,格局生变!