慢慢开始摸索FPGA仿真软件的用法,渐渐熟悉,用起来和C++的IDE也差不多的感觉。

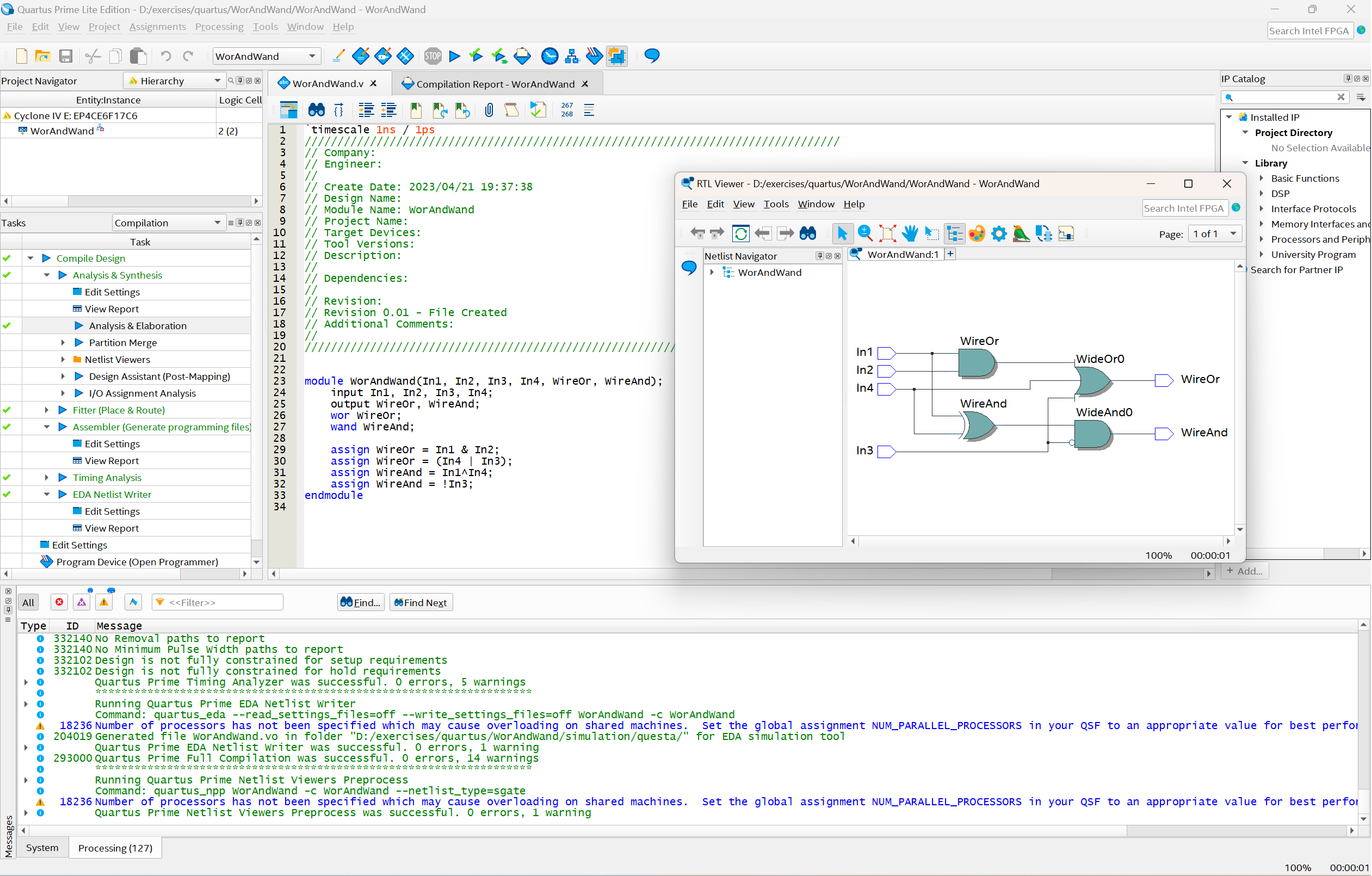

同一段代码,在Quartus下,编译后的逻辑图如下图所示:

这图与我那本N年前在书店5块钱购买的《精通Verilog HDL语言编程》有点不太一样。估计是软件设计改进了。

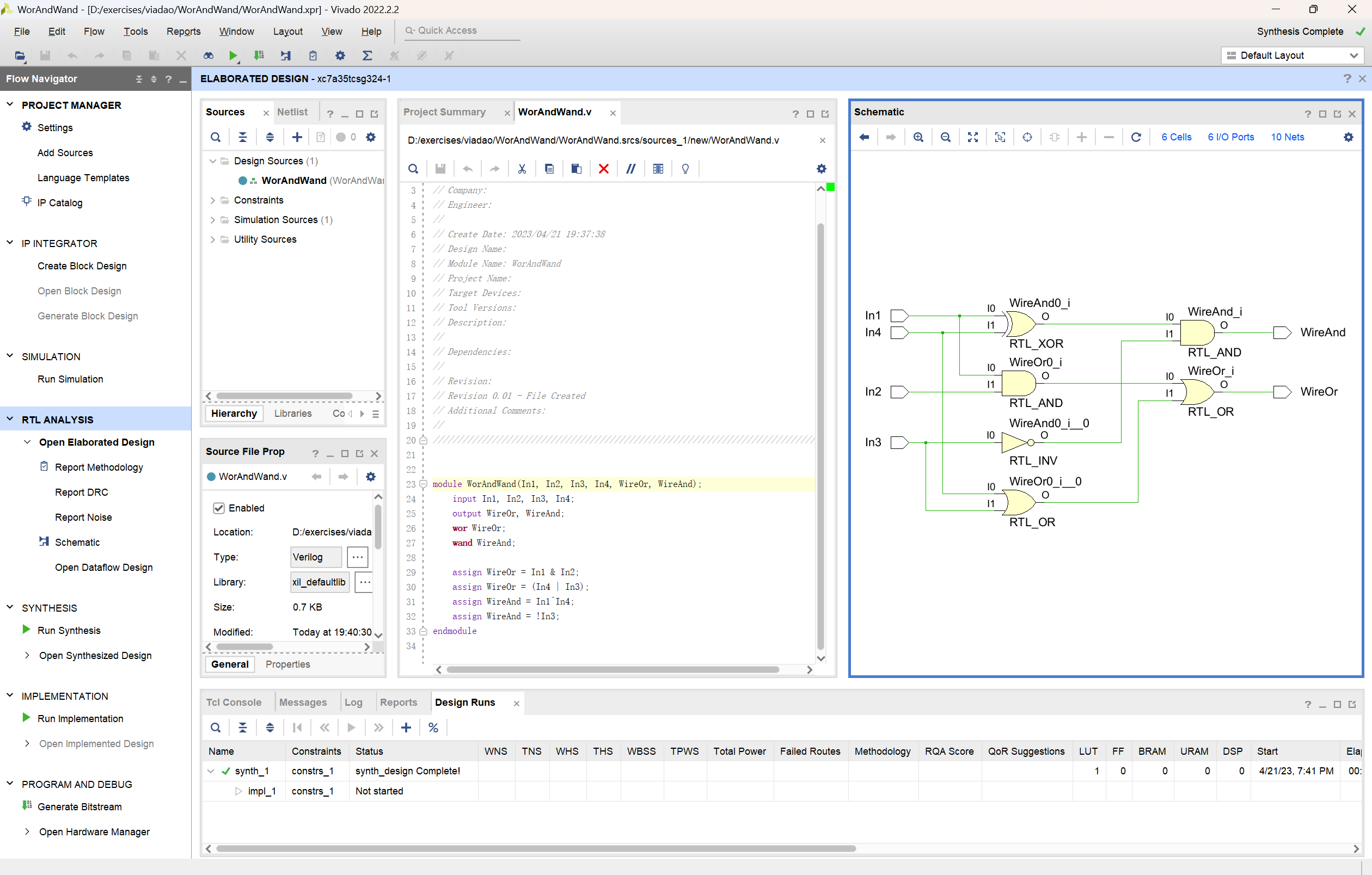

然后,想起来我还安装了VIVADO,那就也试试。实验的时候,才发现VIVADO有两种原理图,一种是综合后的图,使用LUT的,另一种才是逻辑图。逻辑图如下图所示:

这次生成的电路与我那本古书上的电路基本相似了,而且看起来舒服多了,像数字电路教材上的电路画法。

经过我一个星期的摸索,发现,如果想学习数字电路,我是说单纯的学习数字电路的本科教材,不涉及工作和实际应用的情况下,

比如国内的清华版《数字电子技术基础》可能使用Quartus比较好一些,可以直接使用74系列的元件符号搭建仿真电路,而VIVADO则没有74系列的。

但如果,学习国外是数字电路教材,类似《数字设计原理与实践》,可能使用VIVADO好一些,VIVADO生成的电路更漂亮一些,和教材上的电路一致性更高一些。

如果单纯的想学习Verilog语言的语法规则,并且想学习testbench的写法,只使用ModelSim即可。

以上,是我简单摸索一个星期之后,得出来的不知道对错的结论。不过从教材数量上,开发板数量以及各种搜索问题的论坛来看,用Quartus确实比Vivado多。