【学习视频】正点原子https://www.bilibili.com/video/BV11j411f7Co

===================================================================

【学习笔记】

【1】

DDR的帧缓存操作:VDMA写数据至DDR;VDMA再从DDR中读取数据。

作用:解决视频源与显示设备间速率、分辨率不匹配的问题。

【2】

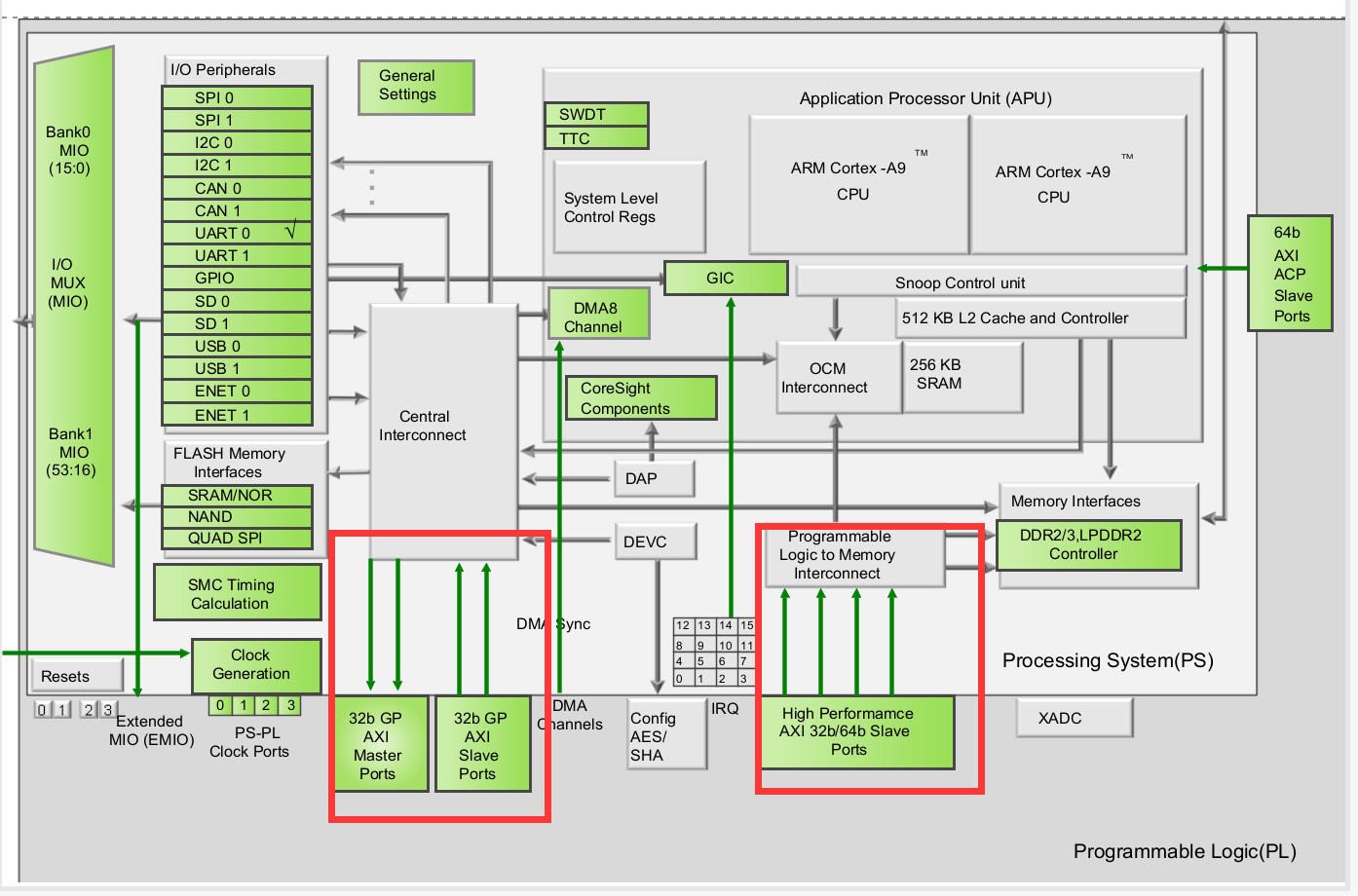

PS通过GP接口控制PL中的VDMA模块。

【3】

打开Vivado工程,新建Block Design,配置ZYNQ-PS:

(1)UART0:14、15

(2)DDR3:MT41J256M16RE-125

(3)FCLK_CLK0:100MHz

(4)HP Slave AXI:HP0(S_AXI_HP0)

对于HP而言,PS是从机,故为Slave,而PL为主机;但在本实验中,PS是GP接口(M_AXI_GP0)的主机,PL为从机。

【4】

HP:High Performance Ports 高性能端口,每个接口有两个FIFO缓存(AFI:AXI FIFO interface)

GP:General Purpose Ports 通用端口(同GPIO),无FIFO缓存

共有四个HP接口,均是PL为主机,PS为从机(箭头从PL指向PS)

共有四个GP接口,两个是PL为主机、PS为从机,两个是PL为从机、PS为主机。(本次实验用到后者之一)

【5】

Interconnect互联:数据交互的主要机制(机构,mechanism,也可称为“开关”,即开启/关闭数据的交互)

互联矩阵:网状结构

【6】

数据总线位宽(Data bus width)

HP:32或64bit(借助FIFO提升了性能)

GP:32bit(无FIFO)